AMD auf dem Weg zum Earnings-Crossover mit Intel (Seite 2347)

eröffnet am 21.04.06 19:39:20 von

neuester Beitrag 02.05.24 15:42:12 von

neuester Beitrag 02.05.24 15:42:12 von

Beiträge: 30.447

ID: 1.055.324

ID: 1.055.324

Aufrufe heute: 159

Gesamt: 2.791.485

Gesamt: 2.791.485

Aktive User: 0

ISIN: US0079031078 · WKN: 863186 · Symbol: AMD

143,06

EUR

-0,35 %

-0,50 EUR

Letzter Kurs 13:12:43 Tradegate

Neuigkeiten

15:55 Uhr · wallstreetONLINE Redaktion |

| Der totale Zusammenbruch von AMD. Reißleine ziehen?Anzeige |

15:00 Uhr · globenewswire |

07.05.24 · BNP Paribas Anzeige |

07.05.24 · globenewswire |

Werte aus der Branche Halbleiter

| Wertpapier | Kurs | Perf. % |

|---|---|---|

| 2,5000 | +119,30 | |

| 45,80 | +13,37 | |

| 0,8400 | +11,96 | |

| 118,00 | +11,13 | |

| 8,0000 | +11,11 |

| Wertpapier | Kurs | Perf. % |

|---|---|---|

| 12,440 | -7,65 | |

| 3,9050 | -8,33 | |

| 24,070 | -8,48 | |

| 68,72 | -9,80 | |

| 2.000,00 | -84,62 |

Beitrag zu dieser Diskussion schreiben

@Variable Vdd

Ist vielleicht für euch interessant:

Power Reduction using LongRun2 in Transmeta's Efficeon Processor

http://transmeta.com/pdfs/presentations/060517_mpf_spring_20…

Ist vielleicht für euch interessant:

Power Reduction using LongRun2 in Transmeta's Efficeon Processor

http://transmeta.com/pdfs/presentations/060517_mpf_spring_20…

Antwort auf Beitrag Nr.: 28.313.086 von BUGGI1000 am 15.03.07 17:36:01@Stefan

Du überschätzt den Einfluss der Spannung auf die Verlustleistung. Die Spannung geht zwar quadratisch ein, aber von einem riesigen Offset aus. Ich habe die Werte mal anhand der dokumentierten Powerstates des SC Turion durchgerechnet, und da kam mit variabler Spannung nicht viel zusätzliches Einsparpotential raus. Der Takt hat den größeren Einfluss, obwohl er nur linear zur Verlustleistung beiträgt. Dafür kann man ihn aber viel tiefer runternehmen. MfG

Du überschätzt den Einfluss der Spannung auf die Verlustleistung. Die Spannung geht zwar quadratisch ein, aber von einem riesigen Offset aus. Ich habe die Werte mal anhand der dokumentierten Powerstates des SC Turion durchgerechnet, und da kam mit variabler Spannung nicht viel zusätzliches Einsparpotential raus. Der Takt hat den größeren Einfluss, obwohl er nur linear zur Verlustleistung beiträgt. Dafür kann man ihn aber viel tiefer runternehmen. MfG

Antwort auf Beitrag Nr.: 28.312.952 von Dresdenboy am 15.03.07 17:29:35@Matthias

Das Problem ist ja auch, dass diese Spannungen von außen kommen u. vom Board erzeugt werden müssen.

Hmm. Ich bin jetzt leider kein guter Elektriker, aber ich dachte es gibt circuitry zuhauf mit der man aus einer Spannung eine andere machen kann. Die kann man entweder auf dem Chip machen (ich ging daon aus dass diese SIMD-Bausteinchen um das Die herum was mit solcher Mimik zu tun haben) oder auf dem die.

Auf der verlinkten Grafik meine ich herauszulesen dass man aus der gemeinsamen VDDNM VDDA, VHT, VDDIO und VTT macht.

Aber es mag wohl so sein dass der Wunsch der Vater des Gedankens ist dass man das für die Cores und ihre Powerstates ebenfalls macht.

Die maximal erreichbaren Takte der Cores ist aufgrund der Nähe zueinander (also auch auf dem Wafer) sowieso ähnlich, da sich das innerhalb eines Wafers eher großflächig unterscheidet.

Die Waferposition spielt eine Rolle, aber ist nur eine von ein paar Dutzend Faktoren wie gut ein Core geht. Ich hab letztes Jahr in Cork auf Irland mit einem Typ gesprochen der sich bei der Evaluierung von Opterons für storage-management mit der Frage beschäftigt hat und die Cores eines X2 getrennt übertaktet hat. Mit allem gleich ging der eine auf drei GHz und der andere auf 2.1 Ghz.

Dafür wäre wohl der Takt sinnvoll, mit dem alle Cores gleichzeitig auf 100% laufen können.

Jo. Ich will gern glauben dass man es so macht: In diesem Licht sehen die Taktfrequenzen von Barcelon die man sich erzählt gleich viel besser aus.

schlecht serialisierbare Probleme gibt es immer wieder Mal.

Die schlecht parallelisierbaren sind tausendmal häufiger, sonst hätten wir wohl schon lange mehr parallelen Code....

K.

Das Problem ist ja auch, dass diese Spannungen von außen kommen u. vom Board erzeugt werden müssen.

Hmm. Ich bin jetzt leider kein guter Elektriker, aber ich dachte es gibt circuitry zuhauf mit der man aus einer Spannung eine andere machen kann. Die kann man entweder auf dem Chip machen (ich ging daon aus dass diese SIMD-Bausteinchen um das Die herum was mit solcher Mimik zu tun haben) oder auf dem die.

Auf der verlinkten Grafik meine ich herauszulesen dass man aus der gemeinsamen VDDNM VDDA, VHT, VDDIO und VTT macht.

Aber es mag wohl so sein dass der Wunsch der Vater des Gedankens ist dass man das für die Cores und ihre Powerstates ebenfalls macht.

Die maximal erreichbaren Takte der Cores ist aufgrund der Nähe zueinander (also auch auf dem Wafer) sowieso ähnlich, da sich das innerhalb eines Wafers eher großflächig unterscheidet.

Die Waferposition spielt eine Rolle, aber ist nur eine von ein paar Dutzend Faktoren wie gut ein Core geht. Ich hab letztes Jahr in Cork auf Irland mit einem Typ gesprochen der sich bei der Evaluierung von Opterons für storage-management mit der Frage beschäftigt hat und die Cores eines X2 getrennt übertaktet hat. Mit allem gleich ging der eine auf drei GHz und der andere auf 2.1 Ghz.

Dafür wäre wohl der Takt sinnvoll, mit dem alle Cores gleichzeitig auf 100% laufen können.

Jo. Ich will gern glauben dass man es so macht: In diesem Licht sehen die Taktfrequenzen von Barcelon die man sich erzählt gleich viel besser aus.

schlecht serialisierbare Probleme gibt es immer wieder Mal.

Die schlecht parallelisierbaren sind tausendmal häufiger, sonst hätten wir wohl schon lange mehr parallelen Code....

K.

Antwort auf Beitrag Nr.: 28.312.562 von Wörns am 15.03.07 17:08:47@Werner

Kann der K8 nicht und der Barcelona wird es auch nicht können.

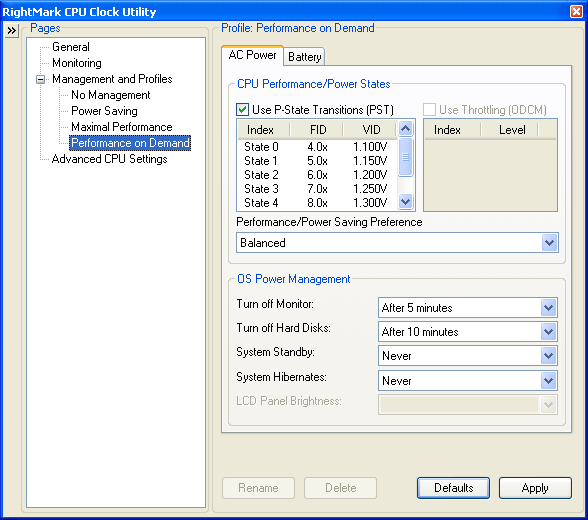

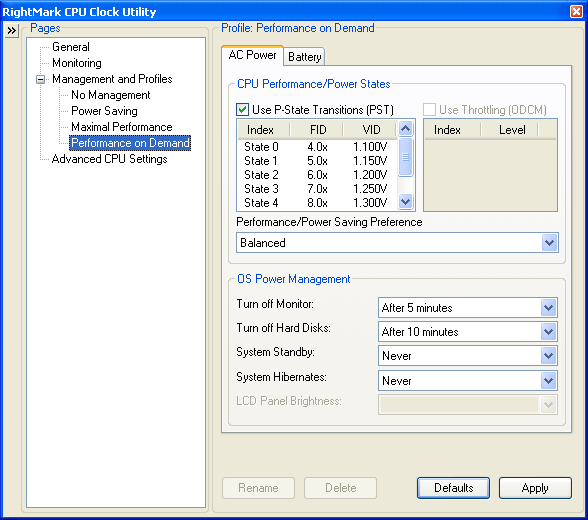

Hmm. Dann müsste ich völlig umdenken. Es würde unter anderem bedeuten dass Dmitris tool nix anderes als hoax wäre.

Möglich ist es. Ich bin schon so viel hoax aufgesessen dass es auf einen mehr oder weniger nicht ankommt. Für die Tatsache dass mein noisebrick mit dem tool eine halbe Stund länger läuft als ohne muss es nicht so funzen wie dmitri es aussehen lässt. Wenn es für alle powerstates die für den höchsten powerstate eingestellte Spannung erzeugt wäre das auch erklärt.

K,

Kann der K8 nicht und der Barcelona wird es auch nicht können.

Hmm. Dann müsste ich völlig umdenken. Es würde unter anderem bedeuten dass Dmitris tool nix anderes als hoax wäre.

Möglich ist es. Ich bin schon so viel hoax aufgesessen dass es auf einen mehr oder weniger nicht ankommt. Für die Tatsache dass mein noisebrick mit dem tool eine halbe Stund länger läuft als ohne muss es nicht so funzen wie dmitri es aussehen lässt. Wenn es für alle powerstates die für den höchsten powerstate eingestellte Spannung erzeugt wäre das auch erklärt.

K,

DDB,

das die Voltage nicht einzeln angepasst werden kann ist sicher

ein Tribut an das Package und den Aufwand, aber langfristig würde

sich sowas lohnen. Man stelle sich dies vor:

QC mit ca. 120W TDP also 30W pro Core (max)

Nimmt man also den Takt im Idle Modus runter, ergäbe sich vielleicht

12-15W pro Core, also bei 3 ungenutzten Cores immer noch runde

40-45W, wenn nur 1 Core Volldampf läuft. In diesem Modus könnten

aber die Spannungen für die 3 Cores dramatisch runter, beispielsweise

von 1,3V auf vielleicht 0,9-1,0V. Damit würde sich eine weitere

Halbierung des Verbrauchs ergeben, also ca. 20W Ersparnis. Garnicht

so übel - oder?

BUGGI

das die Voltage nicht einzeln angepasst werden kann ist sicher

ein Tribut an das Package und den Aufwand, aber langfristig würde

sich sowas lohnen. Man stelle sich dies vor:

QC mit ca. 120W TDP also 30W pro Core (max)

Nimmt man also den Takt im Idle Modus runter, ergäbe sich vielleicht

12-15W pro Core, also bei 3 ungenutzten Cores immer noch runde

40-45W, wenn nur 1 Core Volldampf läuft. In diesem Modus könnten

aber die Spannungen für die 3 Cores dramatisch runter, beispielsweise

von 1,3V auf vielleicht 0,9-1,0V. Damit würde sich eine weitere

Halbierung des Verbrauchs ergeben, also ca. 20W Ersparnis. Garnicht

so übel - oder?

BUGGI

Antwort auf Beitrag Nr.: 28.311.787 von Kpf am 15.03.07 16:27:21@Klaus

Beim Barcelona sind es nur 2 getrennte Planes für die Cores und die NB:

http://enthusiast.hardocp.com/image.html?image=MTE1NjI1MzI3M…

Das Problem ist ja auch, dass diese Spannungen von außen kommen u. vom Board erzeugt werden müssen.

Aber allein die Frequenzanpassung würde schon funktionieren u. da skaliert die Leistungsaufnahme ja etwa linear mit der Frequenz.

Zu den Fragen:

1. Wie implementiert man das? Konfektioniert man so dass jeder Core seine individuelle Maximalfrequenz hat oder stellt man das Management aller Cores auf den Takt ein mit dem der beste davon dauerhaft läuft und throttelt die anderen (durch Einstreuen von Leerzyklen) wenn sie lokal zu heiss werden?

Die maximal erreichbaren Takte der Cores ist aufgrund der Nähe zueinander (also auch auf dem Wafer) sowieso ähnlich, da sich das innerhalb eines Wafers eher großflächig unterscheidet. Damit ist es nicht so wichtig, ob die Maximalfrequenzen getrennt behandelt werden.

Auf jeden Fall würde das Zoned Thermal Monitoring bei diesem Unterfangen deutlich helfen, nahe am Optimum zu arbeiten. Übrigens ist die Temperatur in dem Patentantrag ein Hauptkriterium.

2. Wie kommuniziert man das? Gibt man den höchsten Takt an? Oder macht man bei den Sternenamen etwas ähnliches wie bei Opteron und nimmt Nummern die ihre relative Performance zueinander ausdrückt?

Dafür wäre wohl der Takt sinnvoll, mit dem alle Cores gleichzeitig auf 100% laufen können. HPC-Leute würden CPUs mit 4 Kernen ja nicht danach kaufen, was sie können, wenn man 3 Kerne abschaltet

Das andere Feature wäre eher ein Bonus. Und schlecht serialisierbare Probleme gibt es immer wieder Mal.

Beim Barcelona sind es nur 2 getrennte Planes für die Cores und die NB:

http://enthusiast.hardocp.com/image.html?image=MTE1NjI1MzI3M…

Das Problem ist ja auch, dass diese Spannungen von außen kommen u. vom Board erzeugt werden müssen.

Aber allein die Frequenzanpassung würde schon funktionieren u. da skaliert die Leistungsaufnahme ja etwa linear mit der Frequenz.

Zu den Fragen:

1. Wie implementiert man das? Konfektioniert man so dass jeder Core seine individuelle Maximalfrequenz hat oder stellt man das Management aller Cores auf den Takt ein mit dem der beste davon dauerhaft läuft und throttelt die anderen (durch Einstreuen von Leerzyklen) wenn sie lokal zu heiss werden?

Die maximal erreichbaren Takte der Cores ist aufgrund der Nähe zueinander (also auch auf dem Wafer) sowieso ähnlich, da sich das innerhalb eines Wafers eher großflächig unterscheidet. Damit ist es nicht so wichtig, ob die Maximalfrequenzen getrennt behandelt werden.

Auf jeden Fall würde das Zoned Thermal Monitoring bei diesem Unterfangen deutlich helfen, nahe am Optimum zu arbeiten. Übrigens ist die Temperatur in dem Patentantrag ein Hauptkriterium.

2. Wie kommuniziert man das? Gibt man den höchsten Takt an? Oder macht man bei den Sternenamen etwas ähnliches wie bei Opteron und nimmt Nummern die ihre relative Performance zueinander ausdrückt?

Dafür wäre wohl der Takt sinnvoll, mit dem alle Cores gleichzeitig auf 100% laufen können. HPC-Leute würden CPUs mit 4 Kernen ja nicht danach kaufen, was sie können, wenn man 3 Kerne abschaltet

Das andere Feature wäre eher ein Bonus. Und schlecht serialisierbare Probleme gibt es immer wieder Mal.

Antwort auf Beitrag Nr.: 28.311.787 von Kpf am 15.03.07 16:27:21Verschiede Spannungen fßr verschiedenen Takte (powerstates) kann der K8 (sc) doch schon.[/]

Kann der K8 nicht und der Barcelona wird es auch nicht können.

Bisher geht es nur darum, die Taktfrequenz der Cores separat zu modulieren. Die bisher dürftig veröffentlichten Powerstates (für den SC Turion) betreffen immer Takt und Spannung zusammen. Der Barcelona hat immer eine Spannung für alle Cores, das ist die Spannung des Cores, der den höchsten Takt hat. Die anderen Cores gehen, wenns erlaubt ist, mit dem Takt runter, bleiben aber auf der Spannung. Nebenbei bringts auch gar nicht so viel, die Spannungen zusätzlich zu modulieren.

Die Frage ist, inwieweit der Barcelona die anderen Module (SRQ, XBar, HT-Links, MC) mit eigenen Spannungen versorgen kann und ob er deren Spannungen unabhängig modulieren kann. MfG

Kann der K8 nicht und der Barcelona wird es auch nicht können.

Bisher geht es nur darum, die Taktfrequenz der Cores separat zu modulieren. Die bisher dürftig veröffentlichten Powerstates (für den SC Turion) betreffen immer Takt und Spannung zusammen. Der Barcelona hat immer eine Spannung für alle Cores, das ist die Spannung des Cores, der den höchsten Takt hat. Die anderen Cores gehen, wenns erlaubt ist, mit dem Takt runter, bleiben aber auf der Spannung. Nebenbei bringts auch gar nicht so viel, die Spannungen zusätzlich zu modulieren.

Die Frage ist, inwieweit der Barcelona die anderen Module (SRQ, XBar, HT-Links, MC) mit eigenen Spannungen versorgen kann und ob er deren Spannungen unabhängig modulieren kann. MfG

Gute Zusammenfassung von tgdaily zu Ruiz´s Kommentare bei AMDs Q1-Revenue-Warnung: http://www.tgdaily.com/2007/03/05/amd-quad_core/

Eine Earnungs-Warnung wurde ja eigentlich nicht gegeben, oder? So scheint es auch tgdaily zu sehen:

"...The executive described the switch from a channel- to an OEM-focused business as "dramatic" and as a situation that "we have created for ourselves," but did not indicate that AMD would depart from this strategy anytime soon. He agreed that AMD is currently "challenged" with revenue and profitability, but did not confirm that AMD would be losing money in Q1 and Q2 of this year..."

Und nach den Kommentaren von Ruiz scheint Barcelona vermutlich nicht vor Q3/07, womöglich gar Q4/07, zu kommen...

Doch vermutlich ist Barcelona wirklich viel mehr, als wir bisher erwarteten. Und ebenso vermute ich gar, dass Barcelona über das im von DDB verlinkten Patent geschilderten "Takten innerhalb der TDP" enthalten sein könnte. Womöglich auch daher das große Schweigen über die Takte von K10?

Eine Earnungs-Warnung wurde ja eigentlich nicht gegeben, oder? So scheint es auch tgdaily zu sehen:

"...The executive described the switch from a channel- to an OEM-focused business as "dramatic" and as a situation that "we have created for ourselves," but did not indicate that AMD would depart from this strategy anytime soon. He agreed that AMD is currently "challenged" with revenue and profitability, but did not confirm that AMD would be losing money in Q1 and Q2 of this year..."

Und nach den Kommentaren von Ruiz scheint Barcelona vermutlich nicht vor Q3/07, womöglich gar Q4/07, zu kommen...

Doch vermutlich ist Barcelona wirklich viel mehr, als wir bisher erwarteten. Und ebenso vermute ich gar, dass Barcelona über das im von DDB verlinkten Patent geschilderten "Takten innerhalb der TDP" enthalten sein könnte. Womöglich auch daher das große Schweigen über die Takte von K10?

Womöglich der Grund, weshalb R600 so lange verschoben wurde:

"...Gingen wir bisher davon aus, dass der R600 in 80 nm kommen würde, wurden wir in der exklusiven Runde eines besseren belehrt. Wie es scheint, will AMD den Chip von Anfang an in 65 nm bringen. Grund hierfür seien Probleme bzw. die schlechte Ausbeute des 80 nm Prozesses, der wohl nicht unerhebliche Schwierigkeiten mit Leckströmen haben soll..."

Wie schon von mir vermutet, dürfte Q1/07 vor allem wegen extrem schlechter GPU-Verkäufe so schlecht werden. Das wird nun auch von k-hardware mehr oder minder bestätigt:

"...Abseits der Gerüchte und Spekulationen war zu merken, dass die Stimmung – vor allem auf Seiten von HIS – angespannt war, da man schon seit Weihnachten auf einen Konkurrenz-Chip wartet, der mit der achten GeForce Generation mithalten kann. So kommt es, dass die Verkäufe momentan am Boden liegen, was vor allem für die High-End-Karten gilt, die trotz des günstigen Preises Ladenhüter sind..."

hier: http://www.k-hardware.de/news.php?s=K318002b636e5a8c7e848698…

"...Gingen wir bisher davon aus, dass der R600 in 80 nm kommen würde, wurden wir in der exklusiven Runde eines besseren belehrt. Wie es scheint, will AMD den Chip von Anfang an in 65 nm bringen. Grund hierfür seien Probleme bzw. die schlechte Ausbeute des 80 nm Prozesses, der wohl nicht unerhebliche Schwierigkeiten mit Leckströmen haben soll..."

Wie schon von mir vermutet, dürfte Q1/07 vor allem wegen extrem schlechter GPU-Verkäufe so schlecht werden. Das wird nun auch von k-hardware mehr oder minder bestätigt:

"...Abseits der Gerüchte und Spekulationen war zu merken, dass die Stimmung – vor allem auf Seiten von HIS – angespannt war, da man schon seit Weihnachten auf einen Konkurrenz-Chip wartet, der mit der achten GeForce Generation mithalten kann. So kommt es, dass die Verkäufe momentan am Boden liegen, was vor allem für die High-End-Karten gilt, die trotz des günstigen Preises Ladenhüter sind..."

hier: http://www.k-hardware.de/news.php?s=K318002b636e5a8c7e848698…

Antwort auf Beitrag Nr.: 28.308.579 von Dresdenboy am 15.03.07 13:46:45@Matthias

dann können Frequenz u. Spannung (noch nicht beim Barcelona) angepasst werden,

Es würde mich wundern wenn Barcelona das nicht kann. Verschiede Spannungen fßr verschiedenen Takte (powerstates) kann der K8 (sc) doch schon. Wenn ich es richtig verstanden habe hat Barcelona für jeden Core ein eigenes powerplane. (?) Weil jeder Core auch sein eigenes power-plane hat sollte es eigentlich gehen.

Über ähnliche Dinge hab ich vor einiger Zeit nachgedacht als ich das dfm on Barcelona im Hinblick auf die Differenzierungsmöglichkeiten (sprich: feature-yields) nachzvuollziehen. Weil ich zu vieles davon nicht verstanden habe hab ich nix dazu geschrieben, diese Fragen die damals aufgeworfen wurden passen zu dem Thema:

Prämisse: Weil jeder Core ein eigens Taktmanagement hat kann er mit seinem individuellen Maximaltakt (beschränkt nicht durch den TDP, sondern durch Hotspots in seinem powerplane) betrieben werden.

1. Wie implementiert man das? Konfektioniert man so dass jeder Core seine individuelle Maximalfrequenz hat oder stellt man das Management aller Cores auf den Takt ein mit dem der beste davon dauerhaft läuft und throttelt die anderen (durch Einstreuen von Leerzyklen) wenn sie lokal zu heiss werden?

2. Wie kommuniziert man das? Gibt man den höchsten Takt an? Oder macht man bei den Sternenamen etwas ähnliches wie bei Opteron und nimmt Nummern die ihre relatie Performance zueinander ausdrückt?

K.

dann können Frequenz u. Spannung (noch nicht beim Barcelona) angepasst werden,

Es würde mich wundern wenn Barcelona das nicht kann. Verschiede Spannungen fßr verschiedenen Takte (powerstates) kann der K8 (sc) doch schon. Wenn ich es richtig verstanden habe hat Barcelona für jeden Core ein eigenes powerplane. (?) Weil jeder Core auch sein eigenes power-plane hat sollte es eigentlich gehen.

Über ähnliche Dinge hab ich vor einiger Zeit nachgedacht als ich das dfm on Barcelona im Hinblick auf die Differenzierungsmöglichkeiten (sprich: feature-yields) nachzvuollziehen. Weil ich zu vieles davon nicht verstanden habe hab ich nix dazu geschrieben, diese Fragen die damals aufgeworfen wurden passen zu dem Thema:

Prämisse: Weil jeder Core ein eigens Taktmanagement hat kann er mit seinem individuellen Maximaltakt (beschränkt nicht durch den TDP, sondern durch Hotspots in seinem powerplane) betrieben werden.

1. Wie implementiert man das? Konfektioniert man so dass jeder Core seine individuelle Maximalfrequenz hat oder stellt man das Management aller Cores auf den Takt ein mit dem der beste davon dauerhaft läuft und throttelt die anderen (durch Einstreuen von Leerzyklen) wenn sie lokal zu heiss werden?

2. Wie kommuniziert man das? Gibt man den höchsten Takt an? Oder macht man bei den Sternenamen etwas ähnliches wie bei Opteron und nimmt Nummern die ihre relatie Performance zueinander ausdrückt?

K.

15:55 Uhr · wallstreetONLINE Redaktion · Advanced Micro Devices |

15:00 Uhr · globenewswire · Advanced Micro Devices |

07.05.24 · dpa-AFX · Advanced Micro Devices |

06.05.24 · dpa-AFX · Advanced Micro Devices |

06.05.24 · BörsenNEWS.de · Advanced Micro Devices |